核心定位:描述什么?

这是两者最根本的区别。

(图片来源网络,侵删)

| 特性 | Verilog | C 语言 |

|---|---|---|

| 核心定位 | 硬件描述语言 | 通用高级编程语言 |

| 描述对象 | 描述硬件电路的结构和行为,它关心的是逻辑门、寄存器、数据如何在它们之间流动。 | 描述算法和软件流程,它关心的是变量、函数、数据结构和执行顺序。 |

| 目标 | 最终目标是生成物理电路(ASIC)或可配置的逻辑单元(FPGA)。 | 最终目标是在通用处理器(CPU)上运行,完成计算任务。 |

| 执行模型 | 并发执行,所有的 always 块(或 assign 语句)都是并行运行的,模拟硬件电路中各个部分同时工作的特性。 |

顺序执行,代码从上到下逐行执行,除非遇到分支或循环。 |

关键区别详解

并发性 vs. 顺序性

这是 Verilog 最核心、也最容易让初学者混淆的概念。

-

Verilog (并发) 想象一个真实的电路板,一个LED灯在闪烁,一个蜂鸣器在响,一个CPU在处理数据,这些事件是同时发生的,Verilog 的代码结构就反映了这一点。

// 这两个 always 块是同时并行运行的 always @(posedge clk) begin // 块1:计数器,每个时钟上升沿加1 counter <= counter + 1; end always @(posedge clk) begin // 块2:LED控制,根据计数器的值改变LED状态 if (counter[23] == 1'b1) // 假设第24位变化足够慢 led <= ~led; end在仿真器中,这两个块会同时被时钟的上升沿“唤醒”并执行,它们之间没有先后顺序。

-

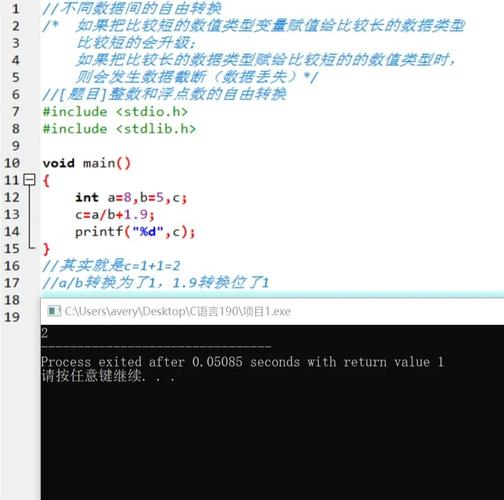

C (顺序) C 代码严格按照书写的顺序执行。

(图片来源网络,侵删)

(图片来源网络,侵删)int counter = 0; int led_state = 0; // 这两行代码是严格顺序执行的 counter = counter + 1; if (counter > 1000000) { // 一个简单的延时 led_state = !led_state; counter = 0; }先执行

counter++,然后才执行if判断。

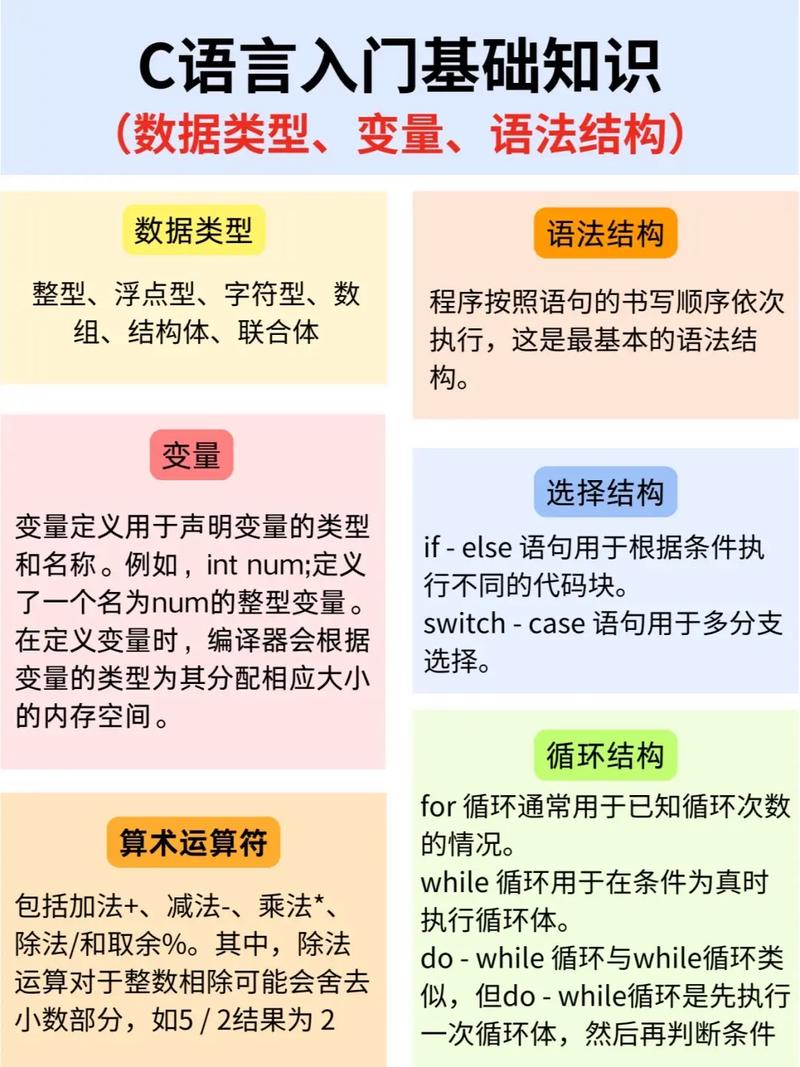

数据类型与变量

-

Verilog

- 物理类型:数据类型直接映射到物理硬件。

wire:表示硬件中的物理连接,比如一根导线,它不能存储值,只能被“驱动”。reg:表示硬件中的寄存器或锁存器,可以存储值,在always块中被赋值。integer:主要用于仿真,不直接映射到硬件(综合器会将其优化掉)。

- 赋值:区分两种赋值符,这非常重要!

- 阻塞赋值,在

always块内,按顺序执行,立即更新值。 <=:非阻塞赋值,在always块结束时,才统一更新所有值,这是组合逻辑和时序逻辑建模的关键,用于避免仿真和实际硬件中的竞争冒险。

- 阻塞赋值,在

- 物理类型:数据类型直接映射到物理硬件。

-

C

- 抽象类型:数据类型是抽象的,由编译器在内存中分配空间。

int,char,float,double等。int *:表示一个内存地址的指针。

- 赋值:只有一种赋值符 ,它表示将右侧的值立即复制到左侧的变量中。

- 抽象类型:数据类型是抽象的,由编译器在内存中分配空间。

执行模型与控制流

-

Verilog

(图片来源网络,侵删)

(图片来源网络,侵删)- 事件驱动:代码的执行由“事件”触发,最常见的是时钟的边沿(

posedge clk,negedge clk)或信号的变化(@a)。 - 结构:

always @(*):用于描述组合逻辑(如加法器、多路选择器),对输入的变化敏感。always @(posedge clk):用于描述时序逻辑(如寄存器、状态机),只在时钟边沿触发。assign:用于描述连续赋值的组合逻辑(如assign y = a & b;)。

- 事件驱动:代码的执行由“事件”触发,最常见的是时钟的边沿(

-

C

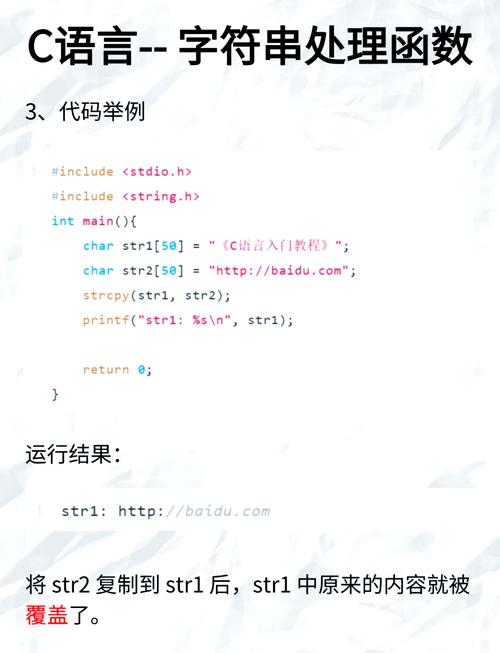

- 指令驱动:代码的执行由CPU按指令顺序执行。

- 结构:

if-else,switch-case:分支结构。for,while,do-while:循环结构。- 函数调用。

内存模型

-

Verilog

- 静态分配:在编译/综合时,变量的内存(即硬件资源,如触发器、LUT)就已经确定好了,没有动态内存分配(如

malloc),因为这无法在硬件上实现。 - 生命周期:变量一旦被声明,其代表的硬件就存在,直到仿真结束或芯片断电。

- 静态分配:在编译/综合时,变量的内存(即硬件资源,如触发器、LUT)就已经确定好了,没有动态内存分配(如

-

C

- 动态/静态分配:既有编译时分配的静态变量/全局变量,也有运行时通过

malloc/new动态分配的堆内存,这给了C语言极大的灵活性,但也带来了内存泄漏等问题。

- 动态/静态分配:既有编译时分配的静态变量/全局变量,也有运行时通过

相似之处

尽管用途不同,但它们在语法上有很多相似之处,这有助于学习。

- 基本运算符:算术运算符 (, , , , )、逻辑运算符 (

&&, , )、关系运算符 (>,<, )、位运算符 (&, , ,^,<<,>>) 等非常相似。 - 条件语句:

if-else和case语句的语法几乎一样。 - 循环结构:

for和while循环的语法也非常相似。 - 注释:都使用 单行注释和 多行注释。

总结表格

| 特性 | Verilog | C 语言 |

|---|---|---|

| 语言类型 | 硬件描述语言 | 通用高级编程语言 |

| 设计目标 | 设计数字电路 | 编写软件应用 |

| 执行模型 | 并发,事件驱动 | 顺序,指令驱动 |

| 基本单元 | 模块 | 函数 |

| 数据类型 | wire, reg (映射物理硬件) |

int, char, float, (抽象内存) |

| 赋值操作 | 阻塞 和非阻塞 <= |

仅 |

| 控制流 | always 块 (组合/时序), assign |

if, for, while, 函数调用 |

| 内存管理 | 静态分配,无 malloc |

静态和动态分配 (malloc) |

| 应用领域 | ASIC/FPGA 设计、芯片验证 | 操作系统、嵌入式、应用软件、驱动程序 |

一个生动的比喻

-

Verilog 就像一份电路原理图,你画了电阻、电容、晶体管,并描述了它们如何连接,你关心的是电流如何同时流过不同的路径,你不能在图上写“先让电流流过电阻,再流过电容”,因为电流是同时存在于所有路径的。

-

C 语言就像一份菜谱,你必须一步一步地写清楚:先放油,再放肉,然后翻炒,你必须严格按照顺序执行这些步骤,才能做出一道菜。

希望这个详细的对比能帮助你清晰地理解 Verilog 和 C 语言的本质区别!